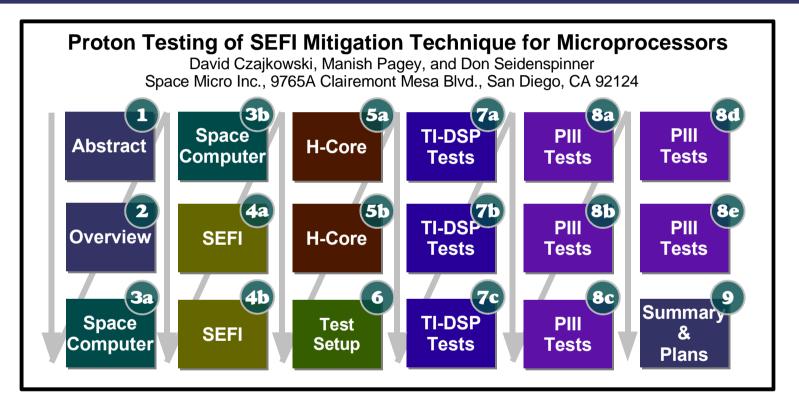

### Abstract

We describe a single event functional interrupt (SEFI) mitigation technique that monitors and maintains the operational status of commercial microprocessors in radiation environments. Proton radiation test results using this technique with an Intel Pentium III microprocessor and a Texas Instruments TMS320C6713 DSP processor are presented.

#### SPACE MICRO INC.

#### Overview

Project partially funded by NASA MSFC as part of a Phase II SBIR.

# Space Micro Inc. Subsystem Background

- \* Rad-Hard satellite computer.

- - △ Over 1000 MIPS throughput,

- ▲ Less than 1 SEU in 1000 days, and

- ▲ Less than 10W power consumption.

- **Building Proton-100k now.**

- **Designed and flew ANTS.**

- **+** Low space orbit balloon testing.

- + Successful balloon launch (Dec.'03).

- Received real-time data and recovered payload.

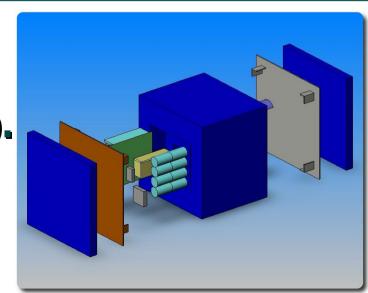

# Proton-100k Space Computer

- **2400 MIPS @ 400 MHz**

- **Over 1440 MIPS with SEU Correction.**

- Less than 1x10<sup>-5</sup> uncorrected SEU

Less than

- **SEFI** mitigation using H-Core™ Chip.

- \* No single event latchup.

- **Total dose hard to over 100krad(Si).**

- **4.9W CPU and 8W total power.**

- + 1GB/s 64-bit DMA bus.

- **PCI/I2C/Parallel bus support.**

- **\$3U cPCI form factor.**

- **VxWorks and Linux OS supported.**

#### **4a**

# Single Event Functional Interrupts

- # EIA/JEDEC Standard No. 57 (1996):

- "The loss of functionality of the device that <u>does not require cycling</u> <u>of the device's power</u> to restore operability unlike SEL and does not result in permanent damage as in SEB."

- SEFIs observed in various complex integrated circuits:

EEPROMs, DRAMs, ADC/DACs, Microprocessors.

- Most common solution for SEFIs is to power cycle the system:

"Even single bit-flips can create circuit-level effects that cause string of errors, or even result in a "lock-up" condition that <u>requires removal of power and subsequent re-initialization</u> to resume proper operation."

-K. LaBel et al., "Emerging Radiation Hardness Assurance Issues: A NASA Approach for Space Flight Programs", 1998.

(http://radhome.gsfc.nasa.gov/radhome/papers/RHA98.pdf)

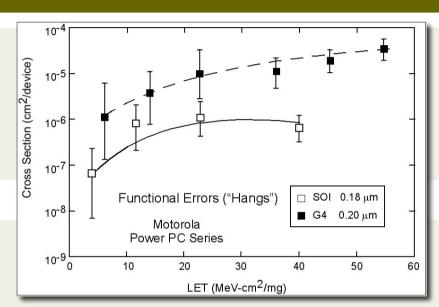

### SEFIS in Microprocessors

- **SEFI Characteristics:**

- Processor "hangs" suddenly.

- △ Observed under proton or heavy ion irradiation.

- **All microprocessors susceptible.**

- Probable causes of "hangs":

- Illegal branching,

- Upsets in program counter of the CPU, and

- ▲ Jump to undefined/test states.

- Approx. rates: 1 per 100 days for SOI PowerPC and 1 per 10 days for the CMOS version.

- SEFI is a severe problem and not easily solvable.

- Current solution to power cycle the system result in unnecessary delays and data loss.

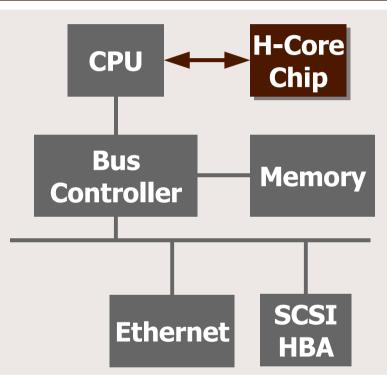

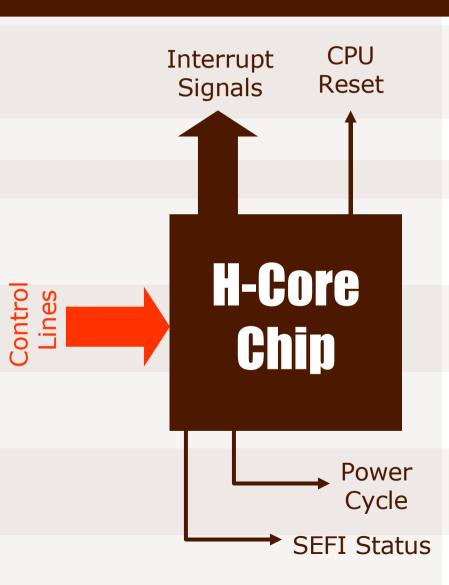

### Hardened-Core Technique

#### + Hardened-Core Chip

- **△ Monitors CPU functionality,**

- **△** Stores rollback information,

- → Detects and indicates SEFI occurrences, and

- → Revives CPU from SEFI events.

#### **+** Hardened-Core Software

- ▲ Sends "CPU alive" messages,

- ▲ Saves periodic roll-back information,

- A Reads SEFI indicator from H-Core chip, and

- ▲ Recovers running processes after SEFI events.

Hardened-Core (H-Core) is a combination of hardware and software techniques that can detect and recover from SEFIs in microprocessors without power cycle or data loss.

### The H-Core Chip

- Manufactured using rad-hard components.

- **Usable with any processor.**

- Provides min. 8 interrupt signals.

- Uses MOSFET driver for power cycle.

- Provides variable levels and pulse widths of interrupts.

- Contains programmable CPUcheck timer.

- Sets SEFI status signal for SEFI recovery software.

- **Provides external reset control.**

#### 6

# Overview of Radiation Experiments

#### **Processors Tested:**

- **△225MHz Texas Instruments TMS320C6713 (TI-DSP)**

- **△850MHz Intel Pentium III (PIII)**

#### **Radiation Facility:**

- → Processor irradiated with 51MeV protons.

### TI-DSP Experimental Setup

#### **TMS320C6713 DSK**

**USB**

#### **Monitor Computer**

- **△ Development board**

- **^ Runs SEFI test loops**

- **△** Communicates using USB-JTAG link.

- **^ PC with Windows 2000.**

- Monitors and controls the TI-DSP board.

### Monitoring TI-DSP Execution

```

; Calculate (var1+var2)-(var3*var4)/var5[orig and mirror]

; sub sum_orig, div_orig, result_orig

0000A3A8 018868C0 SUB.D1 A2,A3,A3

A3

B4

= 000000008

- 000000000

- 00000008

= 00000000

00001BCC

sum mirror, div mirror, result mirror

SUB.D1

A5.A0.A5

00001BD0

result_orig, result_mirror, comparison_result

= 00000020

0000A3B0 00946A78

CMPEQ.L1

[comparison result] b result ok

- 00005149

0000A3B4 80001310

[ A1] B.S1

0xA438

= 00000000

0000A3B8 820C0940

[ A1] MV.D1

A3,A4

0000A3BC 00006000

- 00000000

: Increment the SEU counter.

= 00000000

*seu_count, local_count;

0000A3C0 00100264 LDW.D1T1

*+A4[0x0],A0

CPU Registers

- 00008FD0

1, local_count, local_count;

B4

B5

B6

B7

B8

B9

B10

B11

B12

- 00006520

- 00000004

local_count, *seu_count ;

B14

0000A3CC 00100274

A0,*+A4[0x0]

= 00000254

Source code and

= 0001AFF0

00001BC0

var1, var1_reg

= 00000007

myk

var2, var2_reg

- 00000010

program counter

0000A3C0

var1_reg, var2_reg, sum_ttmr

= 00000734

= 00000000

: Increment the SEU counter.

= 00006520

= 00000400

- 00000254

= 00001BC0

COCCOCER

*seu_count, local_count;

= 0000A3C

= 00000000

0000A3C0 00100264

LDW.D1T1

*+A4[0x0],A0

0000A3C4 00006000

= 00009200

1, local_count, local_count;

= 00000E00

= 00000000

0000A3C8 00002940

A0.0x1.A0

```

- CodeComposer allows remote monitoring of processor.

- + All processor registers can be observed during irradiation.

- **Test loop results are transmitted back to Monitor computer.**

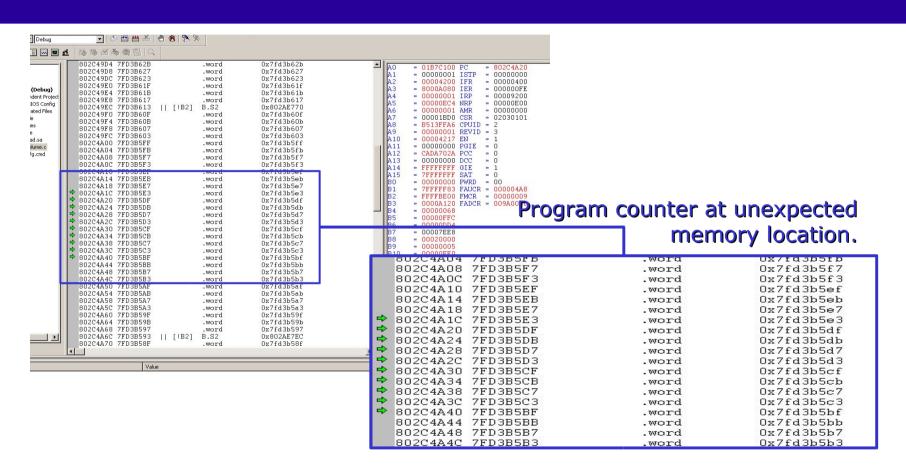

### Signatures of SEFIs

- **Typical SEFI signatures observed during radiation experiment:**

- ▲Jumps to arbitrary memory locations containing random data.

- ▲ Execution of valid instructions that are not part of current program.

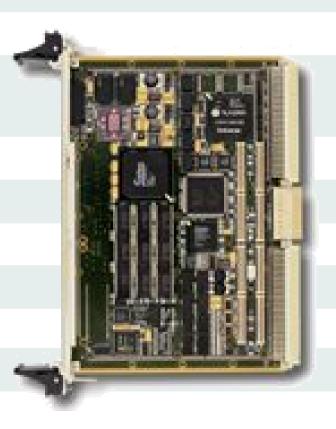

### Intel PIII Experimental Setup

#### **VSBC-8d Test Computer**

- **△** Software/Hardware include:

- SEFI board and test loop,

- Diagnostic self-tests,

- Hardware watchdog, and

- Linux software watchdog.

**RS-232**

**Serial Console**

**Ethernet**

**H-Core Signals**

**Monitor Computer**

- Controls test loops,

- ▲ Sends H-Core signals.

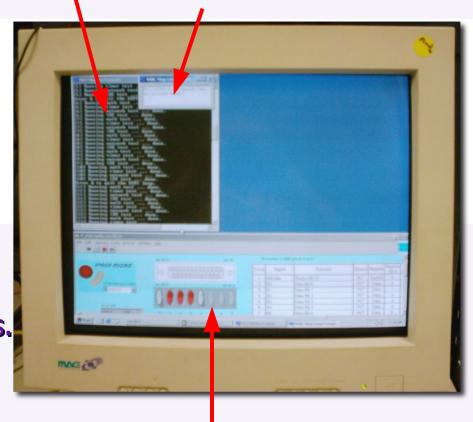

### Test and Monitor Software

#### **VSBC-8d runs Linux OS**

#### **Test loops:**

- ▲ Mathematical functions test.

- **△CPU** timer test.

- Network communication test.

- ▲IDE controller test.

#### **Monitor software:**

- Serial console and telnet.

- Socket communication with test loops.

- ▲ Data logging during irradiation.

- → H-Core signal generation after SEFI.

#### **Monitor software output**

**Test results from VSBC-8d**

**H-Core signal controls**

### H-Core Signals for Intel PIII

**BINIT#** Bus state machine reset.

**+ INIT#** Resets integer registers.

+ LINTO General purpose interrupt signal.

**+ IRQ5** Hardware interrupt through PCI bus.

**+ LINT1** Non-maskable interrupt (NMI).

**RESET#** Intel PIII hardware reset signal.

**Software, hardware, and APIC watchdogs.**

### Irradiation Test Procedure

- 1. Verify test loop results without radiation.

- 2. Start irradiation and monitor test loop results.

- 3. Stop irradiation when incorrect/no test loop results received.

- 4. Assert H-Core signals in sequence to revive the processor.

- 5. CPU assumed to be fully recovered when it responds to a signal.

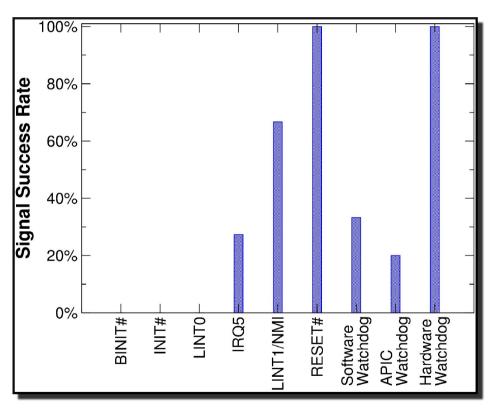

### H-Core Signal Success Rates

#### **SEFI Occurrences and Recovery**

- **△21 SEFIs detected during experiment.**

- ▲ 21 SEFIs recovered using H-Core signals.

- ▲ IRQ5, NMI, and RESET# most effective signals.

- → Presence of software/hardware/APIC watchdog aids recovery.

SEFI mitigation using H-Core technique illustrated for Intel Pentium III processor under proton irradiation.

### Summary and Future Work

#### **Summary**

- Anatomy of SEFI illustrated using proton irradiation of TI-DSP processor.

- → H-Core technique developed for SEFI mitigation.

- → H-Core signals selected for SEFI recovery of Intel PIII processor.

- → Proton irradiation performed on PIII board with H-Core circuit.

- ▲ Processor recovered from all detected SEFIs using H-Core signals without requiring power cycle.

#### **+ Future Work**

- ▲ Development of recovery software after SEFI detection.

- → Proton radiation experiments on multiple processor boards (AMD, PowerPC, and TI-DSP).

- ▲ Incorporate H-Core chip in Proton-100k space computer.

- △ Offer standalone H-Core chip and IP core.